"These slides contain fabricated content and were not generated by or on behalf of AMD" - AMD spokesperson

Yesterday a leaked slide from AMD's upcoming Financial Analyst Day spurred rumors about significantly better single-threaded performance and now the same leaker has published another slide from the presentation that reveals how a Zen unit looks like.

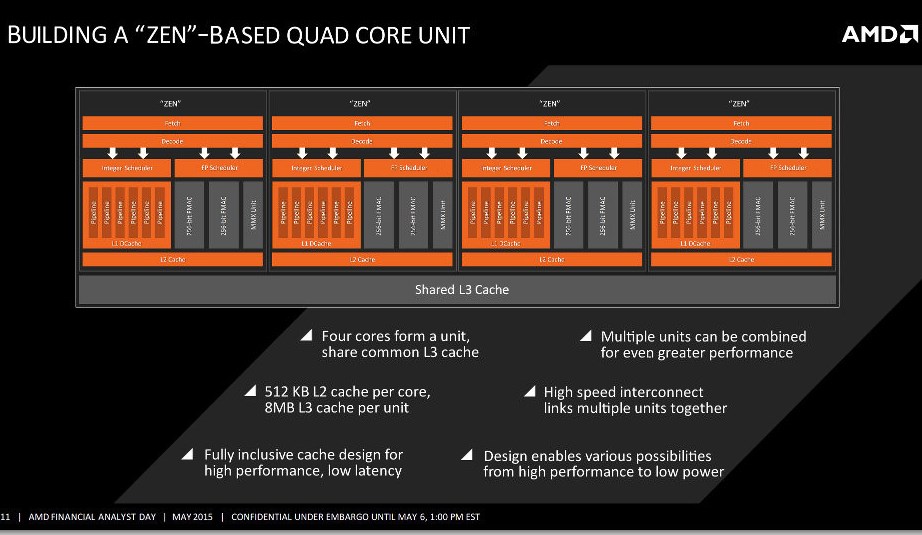

So now we know that a single Zen unit consists of four individual cores tied together with shared L3. Four cores per unit is the maximum but units with less than four cores are also possible. Low-end chips may feature units with two cores disabled for instance, while high-end Zen APUs may combine four units to give you 16 cores.

Each core features up to 512KB L2 cache and each unit has up to 8MB of shared L3 cache. The slide also mentions the use of a high-speed interconnect to link multiple units together and mentions the design enables various possibilities from low power to high performance.