Posted on Monday, October 05 2015 @ 15:30 CEST by Thomas De Maesschalck

Enthusiasts uncovered some new information about AMD's Zen architecture by dissecting a recently released patch file. The information seems to suggest Zen will feature near double as much decoder, ALU, and floating-point units per-core than its predecessor.

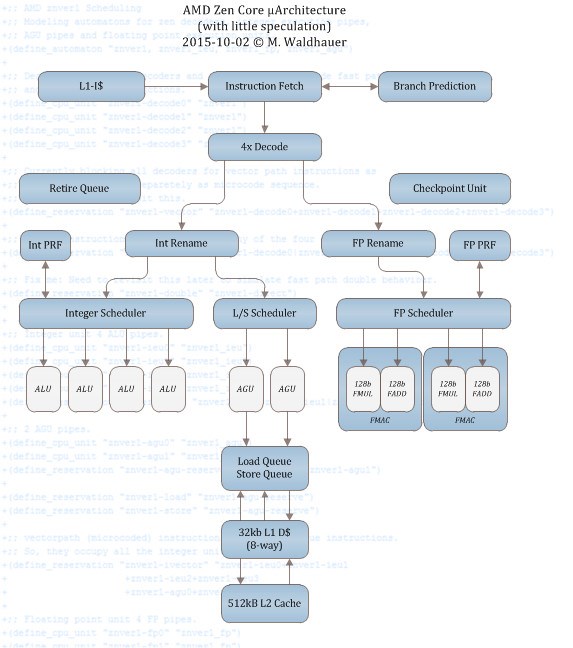

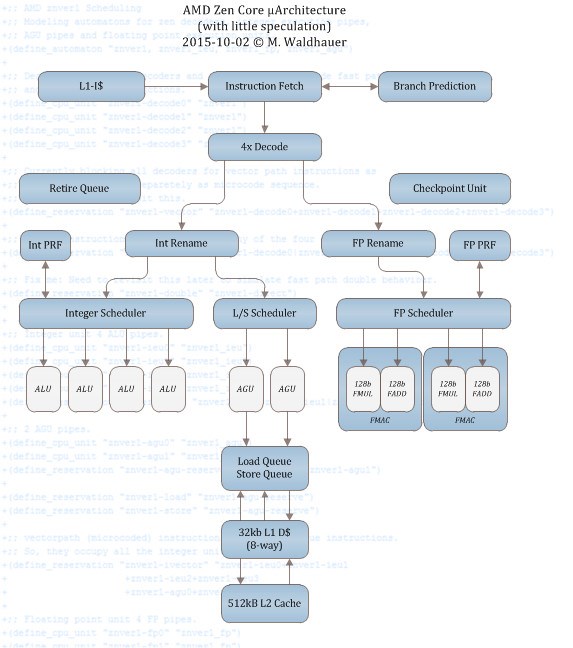

TechPowerUp notes a single Zen core could be described as a Steamroller module with just one big core instead of two, and with support for SMT.

In AMD's latest approach with "Zen," the company did away with the barriers that separated two cores within a module. It's one big monolithic core, with 4 decoders (parts which tell the core what to do), 4 ALUs ("Bulldozer" had two per core), and four 128-bit wide floating-point units, clubbed in two 256-bit FMACs. This approach nearly doubles the per-core number-crunching muscle. AMD implemented an Intel-like SMT technology, which works very similar to HyperThreading.