Posted on Tuesday, December 30 2008 @ 22:58 CET by Thomas De Maesschalck

Techpowerup

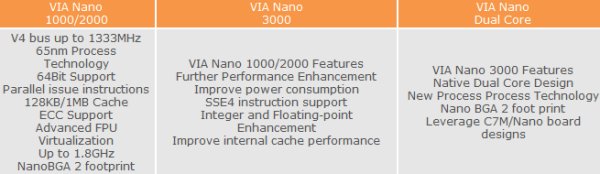

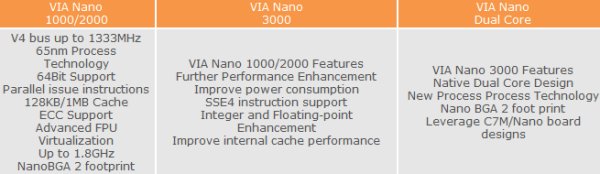

reports VIA is working on a new generation of its Nano processor. The new architecture will be known as Nano 3000, a dual-core version is expected in the second half of 2009 while a single-core model should be available earlier. Both chips will bear the same Nano-BGA package as the current generation.

The processor would use a boarder system interface with the 1333 MHz VIA V4 bus (FSB). It will feature x86-64 extension along with the SSE4 instruction sets to make it standards compliant. It will feature 128KB of L1 and 1MB of L2 caches. VIA is also looking to improve the processor's number-crunching capabilities by working on its integer and floating-point operations efficiency. The processor will be built on the Japanese Fujitsu 65nm manufacturing process which has so far been VIA's foundry partner with processors and S3 Graphics products. The company is also considering a switch to the TSMC 40nm or 45nm node later, sources note.