Posted on Tuesday, August 24 2010 @ 22:01 CEST by Thomas De Maesschalck

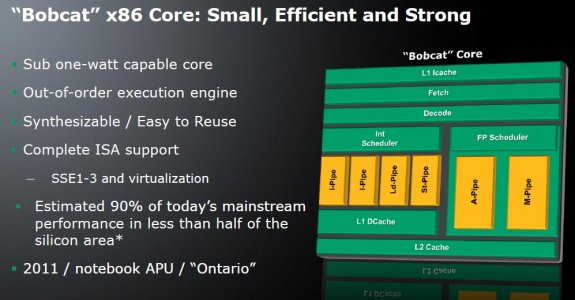

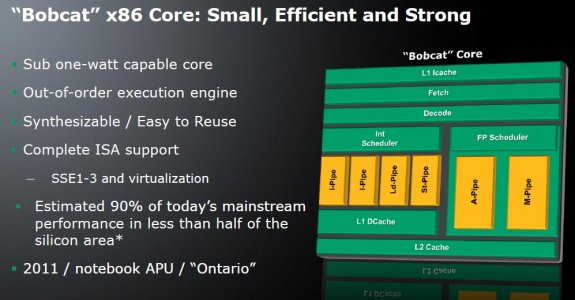

AMD presented architectural details of its Bobcat core at the Hot Chips conference, this is an upcoming processor aimed at low-power consumer market segments. The chip features integrated graphics and enables AMD to create cores that require less than 1W of power. Bobcat is expected to be introduced under the Fusion brand in 2011, it's primarily aimed at netbooks, nettops, and cloud-computing clients.

The GPU doubles up as a raw SIMD engine array that works with applications over OpenCL and ATI Stream technologies to step up performance. The "Bobcat" Fusion APU integrates x86 processor cores with a high-performance switch that doubles up as a memory controller, which connects to a SIMD engine, a UVD display controller, and platform interfaces that include connection to the southbridge chipset and display I/O.

The x86 processor cores are redesigned to cut unnecessary fat (read: caches). It features smaller, but lower latency L1 caches (32 KB L1-I and 32 KB L1-D), advanced branch prediction, full out of the order instruction execution and load/store engines, and a high-performance FPU. The processor supports the AMD64 x86-64 ISA compliant instruction set. As far as SIMD instruction sets go, it seems to have done away with SSE4a and implemented SSSE3 (Supplementary SSE3) ISA instruction set. AMD-V is present to add virtualization support.

More info can be read

at Techpowerup.