Posted on Wednesday, June 27 2012 @ 22:30 CEST by Thomas De Maesschalck

VR Zone delivers news about Intel's 2013-2014 Haswell-EP platform, you can read it

over here. This 22nm server platform may be the first to use DDR4 memory.

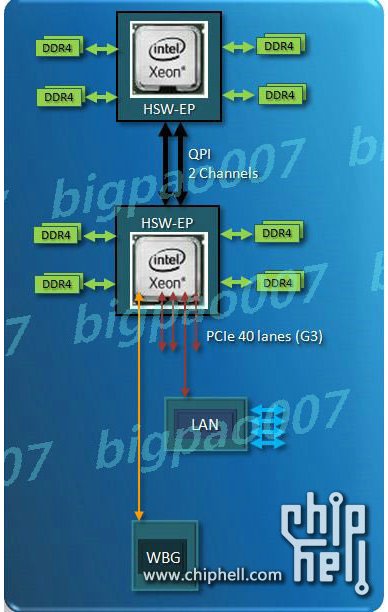

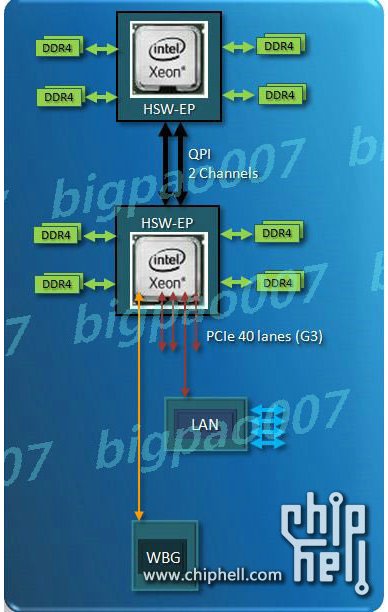

The first and most important portion of a leaked slide reveals the arrangement of the various key components in the platform. It reveals an arrangement that is not much different from today's Sandy Bridge-EP platforms, in which n-number of CPU sockets are wired to each other using fast QuickPath Interconnect (QPI). Intel will use dual-channel QPI, which doubles bandwidth over what is available with today's enterprise platforms. Assuming each channel is clocked at 6.4 GT/s, the cumulative bandwidth would amount to 51.2 GB/s.

Each socket will have four DDR4 DRAM channels. The DDR4 DRAM specification will introduce a fundamental change in the topology of DRAM components, which will be arranged "point-to-point". Each DRAM "channel" from the memory controller will support just one DRAM module, but there will be greater scope for DRAM makers to scale up densities of the modules with advancements in technology and silicon fabrication process. Much like Sandy Bridge-EP, Haswell-EP will see a bulk of the platform's PCI-Express lane budget being care of the processors' system agents; and will require external chipset for peripheral connectivity.