Posted on Thursday, July 19 2012 @ 15:53 CEST by Thomas De Maesschalck

The Register reports Intel accidentally revealed the specifications of its "Poulson" Itanium processors, you can check it out

over here. Known as the Itanium 9500 series, Poulson is anticipated to be launched sometime this year, probably at the Intel Developer Forum in San Francisco in early September.

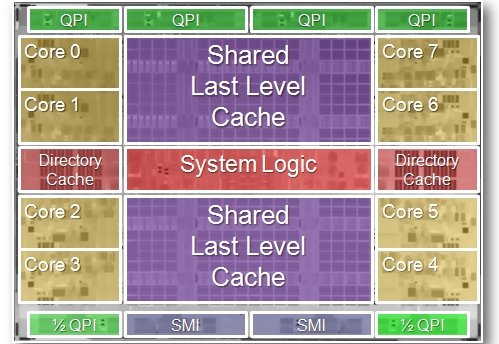

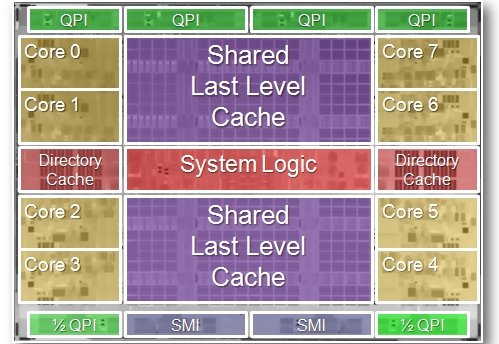

Poulson has eight cores, two directory caches, five QuickPath Interconnect (QPI) links, two Scalable Memory Interconnect (SMI) DDR3 memory controllers that support up to 512GB per socket, two shared L2 caches, and a bunch of system logic all on the same piece of silicon, which has a combined 3.1 billion transistors packed into a 588 square millimeter die size. The top bin part is expected to throw off 170 watts, which is a bit better than the 185 watts of the top-bin four-core Itanium 9300 processor it will replace.

As you can see, the Poulson uses a "cores out" design, just like the current "Sandy Bridge" Xeon E5s, and similarly has a ring interconnect that lashes together the cores, caches, and other elements of the processor.

A Poulson chip has a total of 54MB of SRAM memory: 32MB of L3 cache (broken up into eight blocks, with 4MB for each core), 2MB of total L2 data cache, 4MB of total L2 instruction cache, 2.2MB of directory cache (two chunks), 3.6MB of last level tags, and 169KB of L2 instruction tags. (Intel sometimes calls L2 cache "mid-level cache.")