Posted on Thursday, September 13 2012 @ 14:39 CEST by Thomas De Maesschalck

Speaking at the Intel Developer Forum, Mark Bohr, director of Intel's technology and manufacturing group,

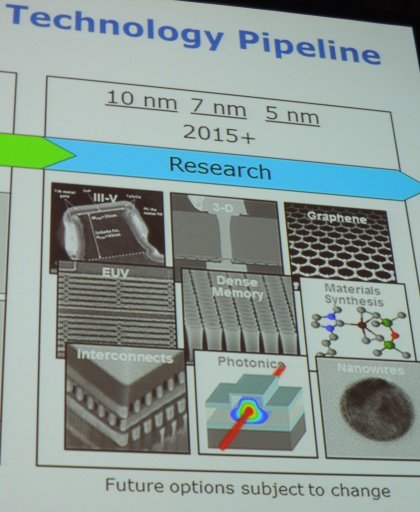

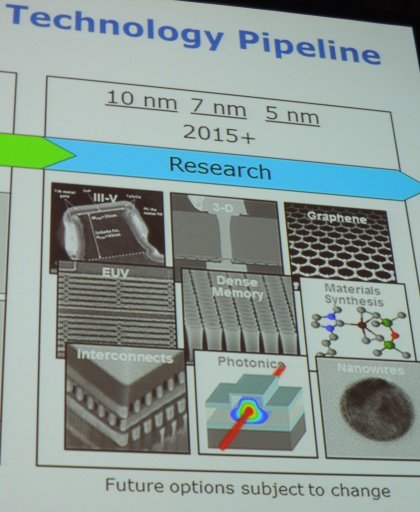

revealed that the chip giant is on track to start making processors on a 14nm process before the end of 2013. Additionally, Bohr also confirmed that Intel has found a way to create a 10nm process technology using immersion lithography. Few details were revealed, but 10nm is anticipated to arrive in 2015 or later. Bohr said 10nm would require quadruple patterning for some mask layers but it's still economical:

Intel expects to use at least double patterning in some layers of some chips at 14 nm. If immersion is used at 10 nm, more layers will require double patterning and some will even require quadruple patterning, he said.

At 14 nm, Bohr said, "the increased wafer costs [associated with double patterning] is still being offset by improved density, so our cost per transistor continues to go down with each generation on a very steady trend,” he said.

That trend would continue, he suggested, even if immersion is used at 10 nm. As of today, “EUV is later than I would like, and I can’t count on it for sure,” he said.

“We are probably the last company continuing to stay on a pace of having a new process technology every two years or so,” Bohr said in his talk.