Made on TSMC's 28nm HPM process, the P5600 supports peak frequencies of over 2GHz. The processor supports up to six cores behind a "coherence manager" that features up to 8MB L2 cache memory. There's 128-bit SIMD computation, hardware-assisted virtualization support , and support for up to a terabyte of RAM via virtual addressing (interesting for server applications)

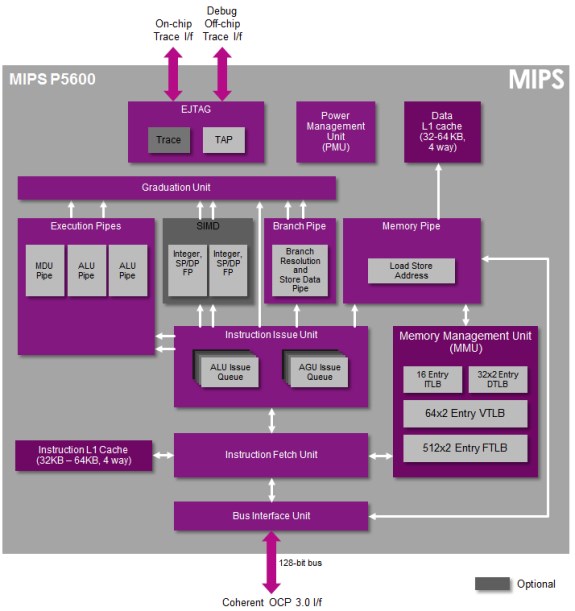

Here’s a breakdown of what to expect from the MIPS P5600 CPU:

Industry-leading single thread performance for high-end 32-bit CPUs (exceeding 5 CoreMark/MHz and 3.5 DMIPS/MHz, per core) at significantly lower power than its competitors Up to 30% area savings at the cluster level and 40% savings at the core level relative to similar performance competition, enabling it to achieve higher performance at reduced area A comprehensive feature set that includes virtualization, 128-bit SIMD, 40-bit eXtended Physical Addressing (XPA), scalable security, and more

The MIPS P5600 IP core is a balanced design that uses techniques such as load/store bonding, reading registers after issue (so no reservation station logic is required), and right-sized schedulers to efficiently achieve maximum utilization of the 16-stage pipeline and its superscalar, multi-issue out-of-order microarchitecture.