It features up to eight ARM Cortex-A57 with a frequency of 2.0GHz and has a TDP range of 15W to 30W.

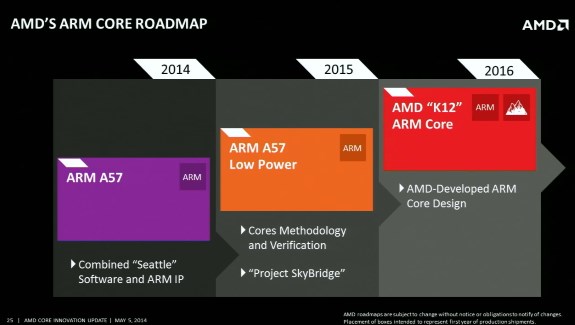

The chip will ship in the SP1 BGA package and features some new cache coherency feature such as full cache coherency, 8 MB L3 cache and SMMU (I/O address, mapping and protection). The chip allows dual channel 64-bit DDR3/DDR4 memory channels (ECC) with speeds of up to 1866 MHz.After that AMD will release SkyBridge, a 20nm platform that features interchangeable 64-bit ARM and x86 low-power APUs with a single pin-compatible socket. And next year AMD will reveal the K12, its in-house high-performance 64-bit ARM core.

The SOC ranges between a TDP of 15 – 30 W. The highly integrated SoC includes 10 Gb KR Ethernet and PCI-Express Gen 3 for high-speed network connectivity, making it ideal for control plane applications. The chip also features a dedicated security processor which enables AMD’s TrustZone technology for enhanced security. There’s also a dedicated cryptographic security co-processor on-board, aligning to the increased need for networked, secure systems.