Posted on Tuesday, April 04 2017 @ 13:30 CEST by Thomas De Maesschalck

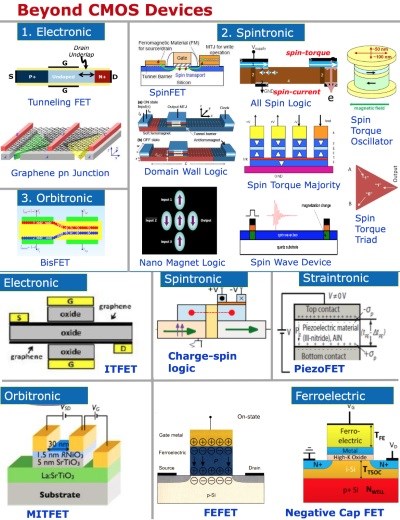

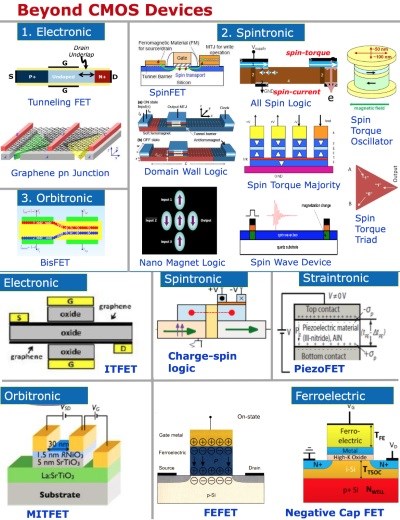

At last month's International Symposium on Physical Design (ISPD 2017), Intel senior fellow Ian Young discussed over a dozen technologies that have the potential to replace the currently used CMOS. Various routes are explored and Intel says the goal is to achieve significantly lower energy use per computational operation while utilizing the same fabs. The latter is a requirement as no matter which technology is adopted, some CMOS transistors will still be needed for certain functionality:

"We are looking beyond CMOS logic and computation methods to discover how to do it differently," said Ian Young, a senior fellow in with Intel's Technology Manufacturing Group and director of exploratory integrated circuits in components research. "We want to lower the power supply voltage well below 0.5V, but the 60mV per decade sub-threshold swing of the MOSFET limits us from doing this for CMOS logic."

The hitch is that no matter which new technology is adopted, it must be integrated with the existing CMOS process because some CMOS transistors will be needed for the clocking and I/O analog circuits. Never fear, however. According to Young, there are around a dozen different ideas being researched to use the same fabs while achieving significantly lower supply voltages.

More details

at EE Times.