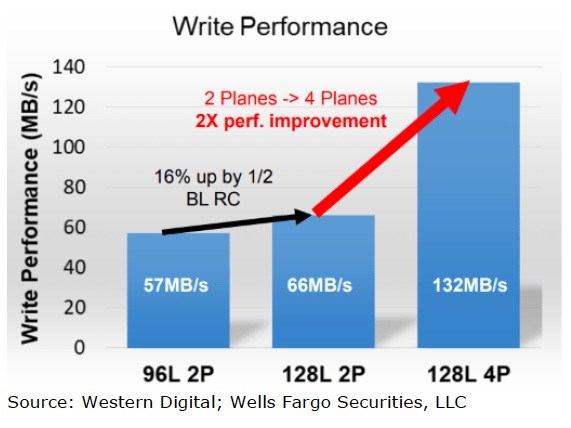

One interesting development here is that the 128-layer 3D NAND from WD and Toshiba will have a 4-plane design. This will roughly double the write performance, as each plane can be independently accessed.

The BiCS-5 chip reportedly features a 4-plane design. Its die is divided into four sections, or planes, which can each be independently accessed; as opposed to BiCS-4 chips that use a 2-plane layout. This reportedly doubles the write performance per unit-channel to 132 MB/s from 66 MB/s. The die also reportedly uses CuA (circuitry under array), a design innovation in which logic circuitry is located in the bottom-most "layer," with data layers stacked above, resulting in 15 percent die-size savings.

Via: TPU