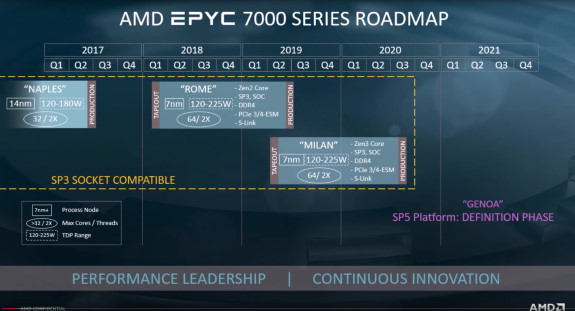

At the event, AMD shared information about its Zen 3 and Zen 4 server architectures. The Zen 3 server architecture is codenamed "Milan" and is already sampling to customers. These chips are made on a 7nm+ process and will hit mass production in Q3 2020.

The Zen 3 based EPYC processors will have the same maximum 64 core count as the current "Rome" chips and they'll support the current SP3 socket. AMD sticks with the same eight-channel DDR4 configuration, PCI Express 4.0 support and a base TDP range of 120W to 225W, but there may also be higher-TDP editions. Tom's Hardware has some more in-depth details here.

However, AMD also disclosed that the company had made a significant alteration to the cache alignments inside the chip, which indicates that there is significant work being done under the hood to improve instruction per cycle (IPC) throughput and reduce latency, both of which are key focus areas for AMD as it evolves its architecture. AMD currently splits its chiplets into two four-core Compute Complexes (CCX), each armed with 16MB of L3 cache. For Milan, that changes to eight cores connected to a unified 32MB slice of L3 cache, which should eliminate a layer of latency within the compute die.AMD also confirmed that Zen 4's codename is Genoa and that these EPYC processors will require the new SP5 socket. Expected sometime in 2021, Zen 4 will support a new memory standard (likely DDR5) and it may also adopt PCI Express 5.0.