Posted on Friday, March 24 2017 @ 18:57 CET by Thomas De Maesschalck

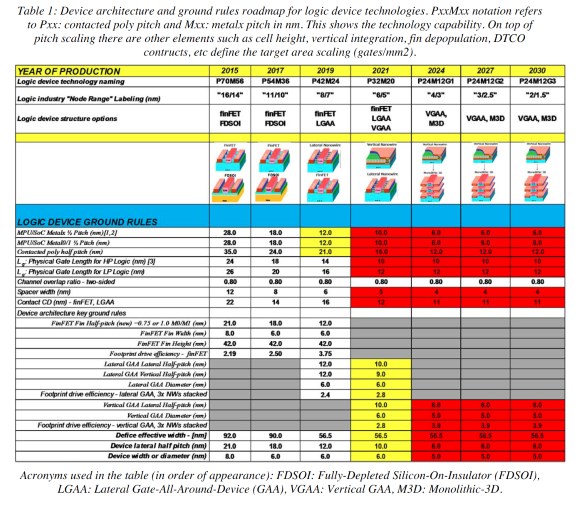

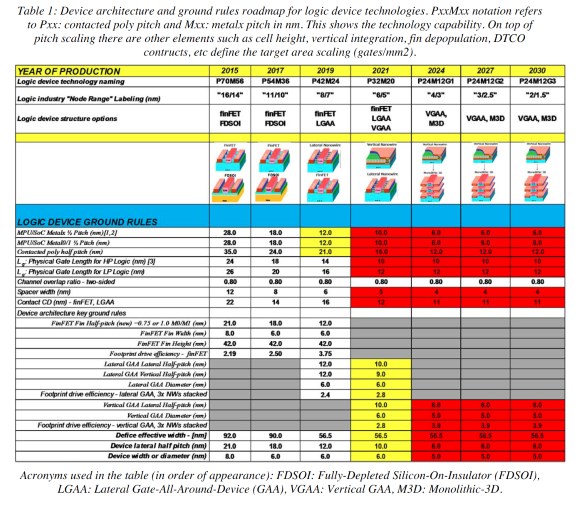

A couple of industry whitepapers reveal semiconductor scaling is expected to reach an end by about 2024. The International Roadmap for Devices and Systems (IRDS) predicts chip makers will be able to hit a node range of 4/3nm, beyond that point it will no longer be physically possible to shrink chips any further.

“Die cost reduction has been enabled so far by concurrent scaling of poly pitch, metal pitch, and cell height scaling. This [will likely] continue until 2024,” according to one of nine white papers published today as part of the International Roadmap for Devices and Systems (IRDS).

Beyond that date “there is no room for contact placement as well as worsening performance as a result of contacted poly pitch (CPP) scaling. It is projected that physical channel length would saturate around 12nm due to worsening electrostatics while CPP would saturate at 24nm to reserve sufficient CD (~11nm) for the device contact providing acceptable parasitics,” the white paper reported.

The report predicts FinFETs will reach their limits a couple of years from now, and suggests the transition to gate-all-around (GAA) transistors could start in 2019, as well as a transition to vertical nanowires. After this, it will be necessary to pursue 3D stacking and monolithic 3D designs to be able to continue to make progress in terms of performance, energy efficiency and cost. Full details can be read

at EE Times, they also discuss some of the new materials that are likely to get adopted.