Posted on Wednesday, August 26 2020 @ 15:21 CEST by Thomas De Maesschalck

Another interesting tidbit from TSMC's technology symposium. AnandTech

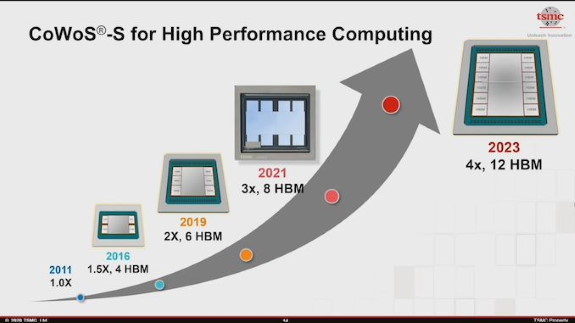

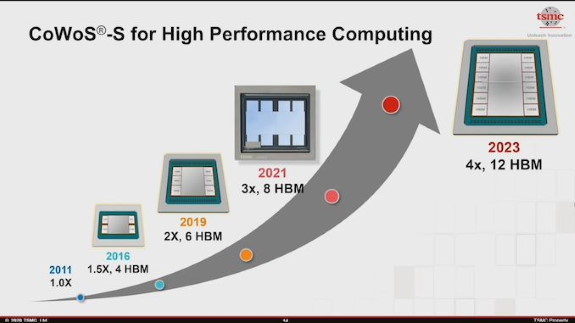

reports the foundry showed a roadmap of its CoWoS-S packaging technology that hints at 3400mm² interposers with twelve stacks of HBM in 2023! Size has been one of the big limitations for complex designs so this should be quite exciting for HPC chip designers.

High-performance computing chip designs have been pushing the ultra-high-end packaging technologies to their limits in the recent years. A solution to the need for extreme bandwidth requirements in the industry has been the shifts towards large designs integrated into silicon interposers, directly connected to high-bandwidth-memory (HBM) stacks.