EE Times has in-depth coverage and reports skeptics are once again doubting whether EUV systems will be able to become mainstream tools for chip makers.

A retired Intel lithographer predicted engineers will be able to create 5nm and even 3nm devices by using two and three passes with an EUV stepper. But a rising tide of chip defects ultimately will drive engineers to new, fault-tolerant processor architectures such as neural networks, said Yan Borovodsky in a keynote at the event.

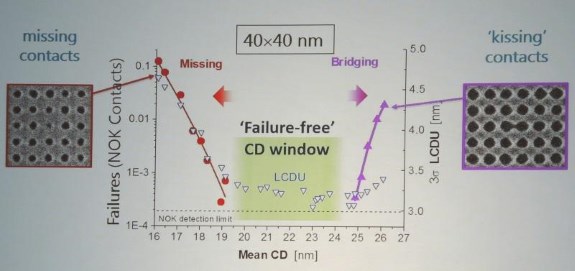

The latest defects are cropping up at critical dimensions around 15nm needed to make 5nm chips for foundry processes targeting 2020. EUV maker ASML is preparing a next-generation EUV system for printing finer features, but those systems won’t be available until about 2024, it said at the event last year.