Besides higher frequency, DDR5 also offers higher memory density. It will be possible to make DDR5 chips with a capacity of 8Gb to 64Gb, whereas the DDR4 standard was limited to a capacity of 2Gb to 16Gb. Next, another big change is that DDR5 will have on-die ECC (Error Correcting Code), this feature will no longer be exclusive to the server market. It does mean that DDR5 will be more expensive, which may be a hindrance to adoption in the mainstream consumer market.

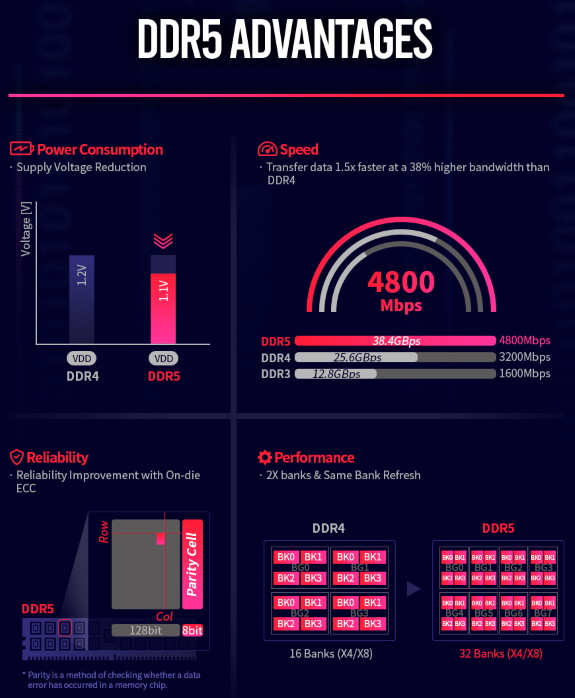

Other changes include a drop in operating voltage from 1.2V for DDR4 to 1.1V for DDR5, double the bank density, and support for same bank refresh. Mass production of SK Hynix' DDR5 will start later this year and initial uptake will be in the server market.

In order to increase the memory bandwidth more than twice compared to DDR4, the amount of data processed within the same unit of time must be doubled. DDR5 will provide increased performance, capacity, and power and cost efficiency previously not available to DDR4, and various features are adopted in DDR5 as below to support the increase of memory bandwidth.

Firstly, DDR5 adopted 32banks structure based on 8 bank groups, which is twice as many as DDR4’s 16banks structure using 4 bank groups. This helped double DDR5’s memory access availability compared to DDR4.

Secondly, DDR5’s burst length (BL)2 is increased to 16 compared to 8 of DDR4, which is another key feature to double memory access availability.

Thirdly, DDR4 cannot perform other operations while refreshing, so it cannot be accessed from the system during refresh timing. However, DDR5 adopted Same Bank Refresh function, allowing the system to access other banks when certain banks are operating, thus improving memory access availability.

Lastly, there are many difficulties in terms of signal integrity with the large number of channels and DIMMs/Sockets in the server system. However, by adopting a Decision Feedback Equalization (DFE) circuit, which eliminates reflective noise during the channels’ high-speed operation, DDR5 increased the speed per pin considerably.