TSX aims to solve part of the performance scaling issue by removing the locks and letting the processor worry about consistency. The thread is executed under the assumption that other threads will not overwrite the variables that the thread is working on, and in case another thread does overwrite one of those shared variables, the whole process will be aborted and re-executed with a traditional lock.

The idea is to remove the locks and let the CPU worry about consistency. Instead of assuming that a thread should always protect the shared data from other threads, you optimistically assume that the other threads will not overwrite the variables that the thread is working on (in the critical section). If another thread overwrites one of those shared variables anyway, the whole process will be aborted by the CPU, and the transaction will be re-executed but with a traditional lock.Software developers will reportedly be able to use the new TSX enabled library with limited code changes, and without having to worry about breaking backwards compatiblity.

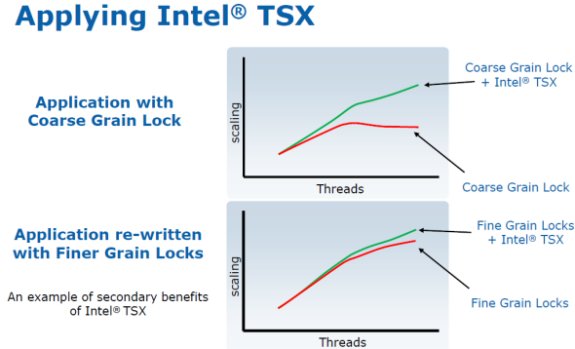

If the lock removing or elision is successful, all threads can work in parallel. If not, you fall back to traditional locking. So the developer can use coarse grained locking (for example locking the entire shared structure) as a "fall back" solution, while Lock Elision can give the performance that software with a well tuned fine grained locking library would get.

Full details at AnandTech.