Posted on Wednesday, February 20 2013 @ 13:17 CET by Thomas De Maesschalck

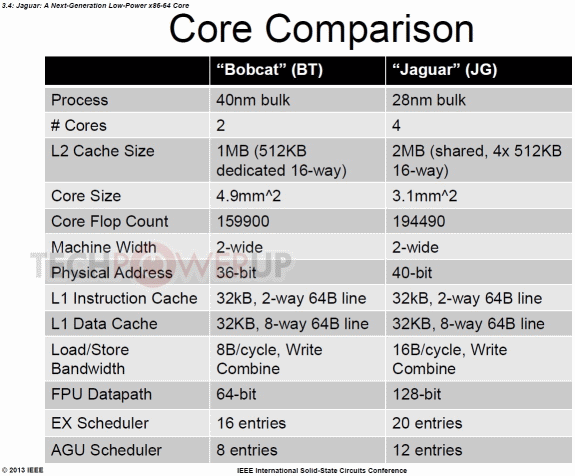

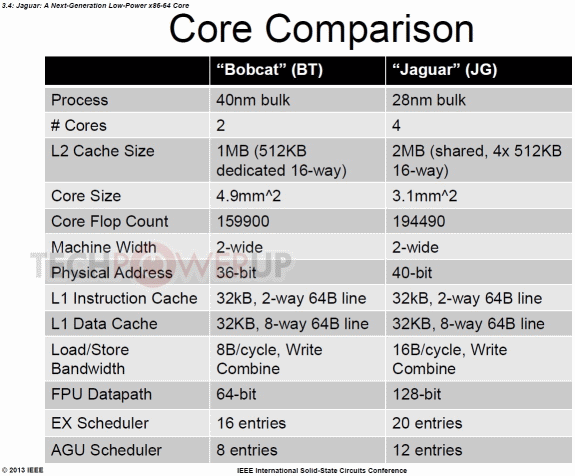

Details about AMD's Jaguar architecture have hit the web. This new core will replace the two-year old Bobcat and will take on Intel's Atom. The Jaguar APU will be offered in TDPs ranging from 5W to 25W, and will target everything from tablets to entry-level notebooks and nettops. AMD presented the Jaguar architecture at the 60th ISSC 2013 conference, the company confirmed that the chip is made on TSMC's 28nm HKMG process and that it has four x86-64 cores that, unlike Bulldozer, are completely independent, they only share a 2MB L2 cache. Full details can be viewed

at TPU.

"Jaguar" x86-64 cores feature a 40-bit wide physical address (Bobcat features 36-bit), 16-byte/cycle load/store bandwidth, which is double that of Bobcat, a 128-bit wide FPU data-path, which again is double that of Bobcat, and about 50 percent bigger scheduler queues. The instruction set is where AMD is looking to rattle Atom. Not only does Jaguar feature out-of-order execution, but also ISA instruction sets found on mainstream CPUs, such as AVX (advanced vector extensions), SIMD instruction sets such as SSSE3, SSE4.1, SSE4.2, and SSE4A, all of which are quite widely adopted by modern media applications. Also added is AES-NI, which accelerates AES data encryption. In the efficiency department, AMD claims to have improved its power-gating technology that completely cuts power to inactive cores, to conserve battery life.