Posted on Monday, August 22 2016 @ 14:47 CEST by Thomas De Maesschalck

More details about the AMD Zen architecture will be revealed at the Hot Chips symposium, but in the meantime you can read

a good piece on AnandTech that dissects everything we know right now.

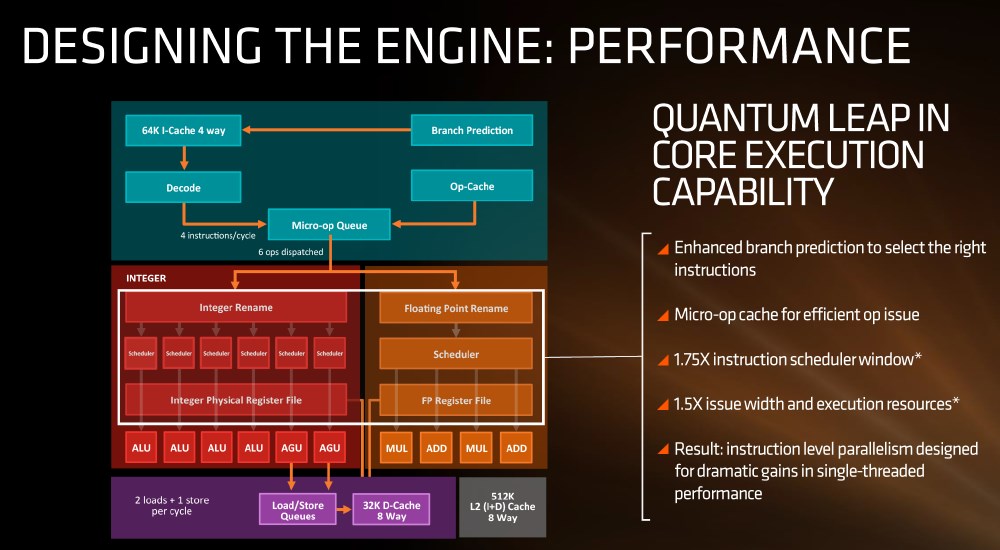

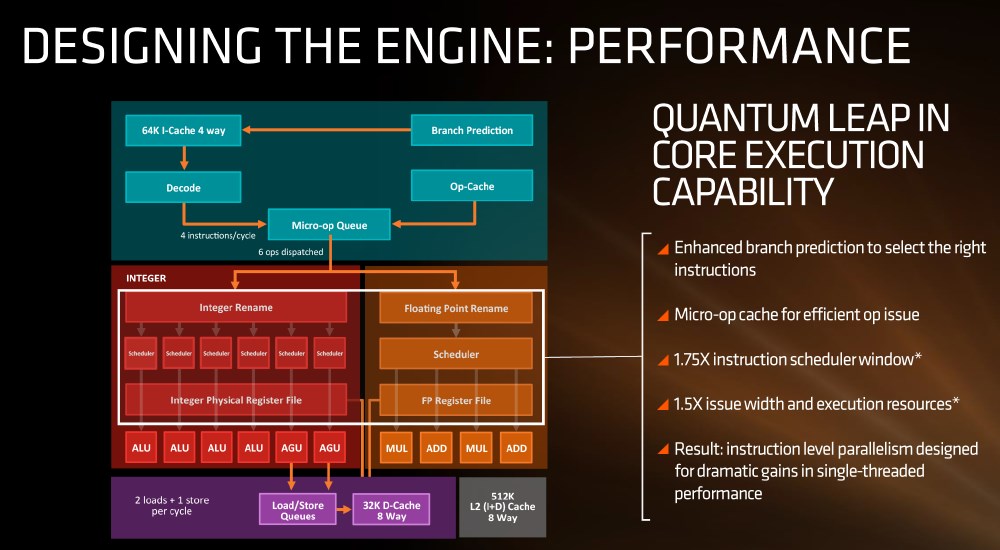

Firstly, one of the bigger deviations from previous AMD microarchitecture designs is the presence of a micro-op cache (it might be worth noting that these slides sometimes say op when it means micro-op, creating a little confusion). AMD’s Bulldozer design did not have an operation cache, requiring it to fetch details from other caches to implement frequently used micro-ops. Intel has been implementing a similar arrangement for several generations to great effect (some put it as a major stepping stone for Conroe), so to see one here is quite promising for AMD. We weren’t told the scale or extent of this buffer, and AMD will perhaps give that information in due course.