Team leader Ali Javey claims the work shows that with proper material choice, there's still a lot of room to shrink electronics to smaller nodes, and that this transistor illustrates there's a path beyond 5nm. You can read more about how they created thi transistor over here.

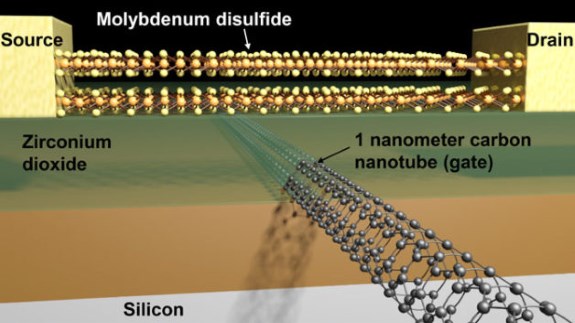

“The semiconductor industry has long assumed that any gate below 5 nanometers wouldn’t work, so anything below that was not even considered,” said study lead author Sujay Desai, a graduate student in Javey’s lab. “This research shows that sub-5-nanometer gates should not be discounted. Industry has been squeezing every last bit of capability out of silicon. By changing the material from silicon to MoS2, we can make a transistor with a gate that is just 1 nanometer in length, and operate it like a switch.”

...

“This work demonstrated the shortest transistor ever,” said Javey, who is also a UC Berkeley professor of electrical engineering and computer sciences. “However, it’s a proof of concept. We have not yet packed these transistors onto a chip, and we haven’t done this billions of times over. We also have not developed self-aligned fabrication schemes for reducing parasitic resistances in the device. But this work is important to show that we are no longer limited to a 5-nanometer gate for our transistors. Moore’s Law can continue a while longer by proper engineering of the semiconductor material and device architecture.”