Posted on Tuesday, January 30 2007 @ 1:25 CET by Thomas De Maesschalck

With its quad-core 45nm Penryn processors Intel will continue

with its dual-die strategy. According to the Inq it may take until Nehalem before the chip giant will have a native quad-core processor.

There may be no chance of a native quad-core product until Nehalem. We hoped to see Intel do something about that, like say put four cores, each with say 2MB L2 cache, plus a shared 16MB L3 cache, on a single 1+ billion transistor die - or, at least, as we mentioned before, do a simple quad-core with a single 8MB shared L2 between them (however, multi-porting and ultrahigh bandwidth required may prove to be a challenge there).

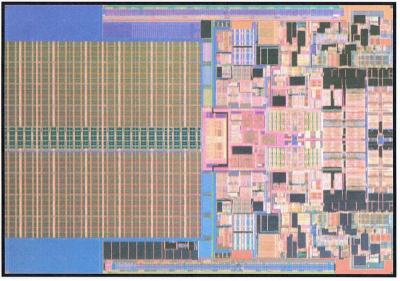

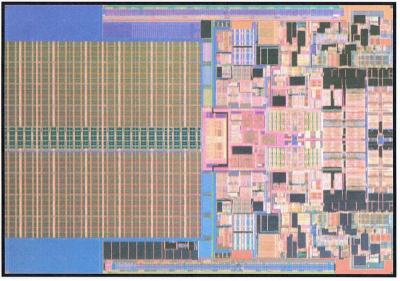

Here's a picture of a dual-core Penryn die. Intel uses two of these to make a quad-core Penryn processor: