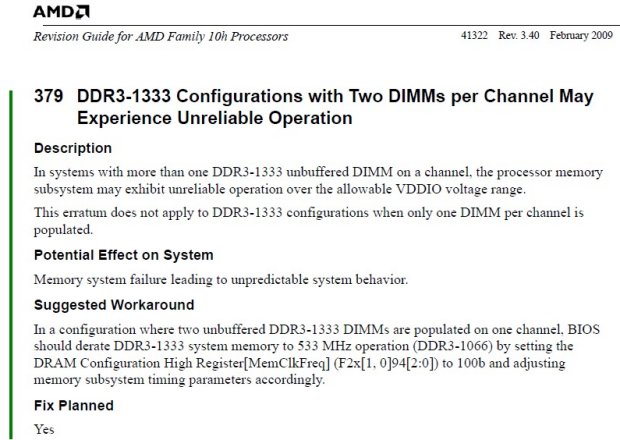

In a revision guide for the AMD Family 10h processors, the chip firm explains they're working on a fix and suggests to underclock your memory to DDR3-1066 in configurations where two DDR3-1333 modules are installed on one channel.

The AMD K10 memory controllers on AM3-socket processor provide a 128-bit wide memory interface (with DRAM Ganged mode enabled), which amount to two 64-bit wide memory channels. On most motherboards, four DIMM slots with two slots sharing a memory channel are present. With this issue, one is not recommended to use more than one DDR3-1333 memory module per channel. AMD recommends a quick fix for the issue for systems using more than one DDR3-1333 module per memory channel: to manually specify the memory to run at 533 MHz (1066 MHz DDR), and accordingly set DRAM timings. As a little compensation, one can tighten DRAM timings with the drop in frequency. AMD will fix this issue in the next stepping (sub-version) of the CPUs. The "x-factor" with this erratum revolves around DRAM voltage, a significant factor. One might note AMD saying "the processor memory subsystem may exhibit unreliable operation over the allowable VDDIO voltage range", which leads us to think if there is a potential workaround with adjusting the DRAM voltage beyond the allowable range (read: over-volting the memory).