Korner says full dual-core optimization means Yonah will feature low power, smart thermal and power management, and elimination of redundant logic.

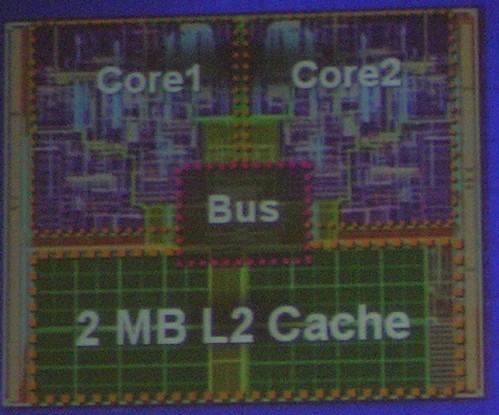

He said that improving media performance is a complex architecture task. Intel profiled a lot of apps running on Dothan and what it learned from these, it improved the architecture to optimize them. Better decoder bandwidth meant the Micro OP Fusion was extended to SSE2 LD-OP instructions, and the 128 bit SSE2 instructions are now handled by all three decoders which Korner claimed gives up to three times decoder bandwidth.Both Yonah cores use the full size shared L2 cache, with shared data accessed from te cache minimizing the buss traffic. The chip also includes dynamic cache allocation.

Korner further added Yonah will deliver a longer battery life over the previous Dothan and Banias Pentium M cores by utilizing techniques such as Vcc cache design. Each core also has its own sleep state, controlled by the OS using the new MWAIT (Cx) instruction.

There's also a derivative of the Yonah targeted at low power blade and rack servers. This will be Sossaman, supporting up to 64GB of memory. More info at The Inquirer