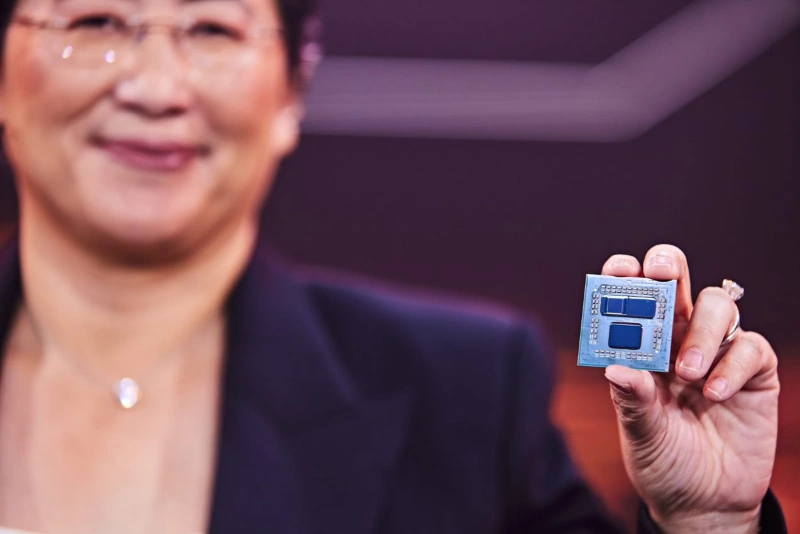

During today's Computex 2021 keynote, AMD CEO Lisa Su revealed a prototype of a Ryzen 5000 series processor with 3D Vertical Cache. This prototype uses a new 3D chiplet technology and AMD claims it will enter production by the end of this year. This lines up perfectly with recent rumors, that the current Vermeer-based Ryzen 5000 series will be succeeded by a Zen 3+ based part called "Warhol".

The new 3D chiplet technology, developed in cooperation with TSMC, enables the bonding of 64MB of 7nm SRAM cache directly onto each core complex. This triples the cache per Zen 3 core. According to AMD, you get a 200x improvement in interconnect density, 15x better density than other chip stacking technologies, superior thermal performance, and 2TB/s of bandwidth.

AMD CEO Lisa Su claims the new 3D Vertical Cache delivers an average performance gain of 15 percent for 1080p gaming. This is the performance advantage AMD observed versus the Ryzen 9 5900X, with both chips clocked at 4.0GHz. If true, AMD has managed to deliver a full architecture generation jump worth of performance gains with 3D Vertical Cache.

AnandTech has extra technical details over here.

That means that the original Ryzen 5000 chiplet, with eight cores having access to 32 MB of L3 cache, now becomes an eight-core complex with access to 96 MB of L3 cache. The two dies are bonded with Through Silicon Vias (TSVs), passing power and data between the two. AMD claims that the total bandwidth of the L3 cache increases to beyond 2 TB/sec, which would technically be faster than the L1 cache on the die (but with higher latency).